# ACS APPLIED MATERIALS & INTERFACES

# High-Quality Solution-Processed Silicon Oxide Gate Dielectric Applied on Indium Oxide Based Thin-Film Transistors

Felix Jaehnike,\*<sup>,†,‡</sup> Duy Vu Pham,<sup>†</sup> Ralf Anselmann,<sup>†</sup> Claudia Bock,<sup>‡</sup> and Ulrich Kunze<sup>‡</sup>

<sup>†</sup>Evonik Industries AG, 45772 Marl, Germany

<sup>‡</sup>Lehrstuhl für Werkstoffe und Nanoelektronik, Ruhr-Universität Bochum, 44801 Bochum, Germany

Supporting Information

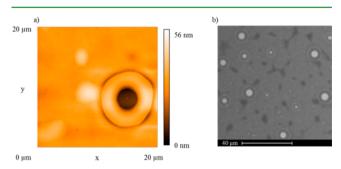

ABSTRACT: A silicon oxide gate dielectric was synthesized by a facile sol-gel reaction and applied to solution-processed indium oxide based thin-film transistors (TFTs). The SiO<sub>x</sub> sol-gel was spin-coated on highly doped silicon substrates and converted to a dense dielectric film with a smooth surface at a maximum processing temperature of T = 350 °C. The synthesis was systematically improved, so that the solution-processed silicon oxide finally achieved comparable break downfield strength (7 MV/cm) and leakage current densities (<10 nA/cm<sup>2</sup> at 1 MV/cm) to thermally grown silicon dioxide (SiO<sub>2</sub>). The good quality of the dielectric layer was successfully proven in bottom-gate, bottom-contact metal oxide TFTs and compared to reference TFTs with thermally grown SiO<sub>2</sub>. Both transistor types have field-effect mobility values as high as  $28 \text{ cm}^2/(\text{Vs})$  with an on/off current ratio of  $10^8$ , subthreshold swings of 0.30 and 0.37 V/dec, respectively, and a threshold voltage close to zero. The good device performance could be attributed to the smooth dielectric/ semiconductor interface and low interface trap density. Thus, the sol-gel-derived SiO<sub>2</sub> is a

**KEYWORDS:** sol-gel, silicon oxide, solution-processed, thin-film transistor, indium oxide, high mobility

# INTRODUCTION

Since the early 1990s, a new rapidly developing economy has come into the focus of research and development: macroelectronics.<sup>1,2</sup> Unfortunately, up to now, current liquid-crystal displays (LCDs) are manufactured by cost-intensive vacuum processes like sputtering and chemical vapor deposition techniques,<sup>3</sup> which include some limitations in mass production and in realization in large-area electronics. For this reason, intensive research has been done in the development of solution-processed metal oxide films because of its simplicity, low cost, and high performance. These films are promising candidates to replace amorphous silicon as the active layer used in thin-film transistors (TFTs) as a switching device, e.g., for display applications and optoelectronic devices.<sup>4-7</sup> Indium oxide based TFTs provide high mobility, which is necessary for advanced display technologies such as 8K ultrahigh-definition, large-size televisions and organic light-emitting diode (OLED) displays.6,8

While solution-processed metal oxide semiconductors have made enormous progress in the past few years,<sup>9-11</sup> there is less research activity toward the development of solution-based novel dielectrics; only a few comprise both.<sup>3,12-14</sup> Most reports on solution-processed semiconductors were made on thermally grown silicon dioxide (SiO<sub>2</sub>) or vacuum-deposited dielectrics.<sup>15-18</sup> To deposit the gate dielectric from a liquid phase, sol-gel chemistry offers a simple method to synthesize solutions for dielectric films and to tune the properties of the resulting product.<sup>8</sup> In many studies concerning solutionprocessed gate dielectrics, several deposition steps are necessary to achieve a desirable film thickness and low leakage currents.<sup>3,19,20</sup> This increases the process complexity and manufacturing costs. Here, we use just one deposition step to achieve desirable dielectric properties like high electric breakdown field strength, low leakage current, and low interface trap density, which is essential for high-performance electronics.<sup>21</sup> Comparable studies on solution-processed silicon oxide achieved leakage current densities that were 2 orders of magnitude higher<sup>22,23</sup> or required considerably higher annealing temperatures ( $T > 450 \ ^{\circ}C$ ) to achieve similar results.<sup>11</sup> This is not suitable for high-performance (flexible) electronic devices. Although the synthesis route of the sol-gel-derived silicon oxide in this paper is similar to that presented in the paper of Cavas et al., the properties (dielectric constant, refractive index, and surface roughness) presented by Cavas et al. are far away from those of thermally grown SiO<sub>2</sub>.<sup>24</sup> A study concerning the influence and role of the material composition and processing parameters of the sol-gel has been completely missing until now.

In this study, we synthesized a solution-processed silicon oxide by a facile sol-gel reaction. The dielectric properties nearly achieved the results obtained from thermally grown SiO<sub>2</sub>. By optimizing the synthesis and processing technique, we achieved leakage current densities of less than  $1 \times 10^{-8}$  A/cm<sup>2</sup> at an applied electric field of 1 MV/cm with a maximum

```

Received: April 10, 2015

Accepted: June 3, 2015

Published: June 3, 2015

```

## **ACS Applied Materials & Interfaces**

annealing temperature of 350 °C. To investigate the quality of the insulator in an electronic device, we combined this solution-processed SiO<sub>2</sub> with the solution-processed indium oxide based semiconductor iXsenic S (provided by Evonik Industries AG) to prepare high-performance TFTs.<sup>25–29</sup> The devices exhibit a mobility of 28 cm<sup>2</sup>/(Vs), an on/off ratio above 10<sup>8</sup>, no hysteresis, and a subthreshold swing of about 0.30 V/dec.

## EXPERIMENTAL SECTION

The sol-gel solution was synthesized by dissolving 0.52 g of tetraethyl orthosilicate (TEOS; Sigma-Aldrich, 99.999% trace metals basis) in 1.0 g of isopropyl alcohol (IPA; Sigma-Aldrich, anhydrous 99.5%), 0.1 g of deionized water, and 0.1 g of 0.1 M nitric acid (Sigma-Aldrich). The whole solution was stirred at room temperature for 5 min. After that, the solution was diluted with 1.28 g of IPA and stirred again for 2 min. Finally, the solution aged for about 6.5 h at room temperature before it was spin-coated on highly p<sup>+</sup>-doped silicon substrates. The dielectric properties were characterized in a metal-insulator-semiconductor (MIS) structure. Therefore, the substrates were cleaned in a standard cleaning process with acetone and IPA. Additionally, the substrates were placed for 10 min in an ozone cleaner to remove organic residuals from the surface and to improve the wettability. Subsequently, 100  $\mu$ L of the sol-gel solution was dropped onto the substrate and spin-coated at 2000 rpm for 30 s. Conversion of the solgel to a dense silicon oxide film was done stepwise: First of all, the substrates were placed on a hot plate at 120 °C for 10 min to slowly evaporate the containing water and the solvent. Next, the film was cross-linked under UV light for 10 min in the ozone cleaner and then annealed on a hot plate at 210 °C for 10 min. The final curing was done for 30 min at 350 °C. For the metal contacts, 80 nm of aluminum were thermally evaporated through a shadow mask in an EB3 thermal evaporator from BOC Edwards Ltd. The contact area of the resulting pads was 1.2 mm<sup>2</sup>.

The bottom-gate, bottom-contact TFTs were processed on an n<sup>+</sup> silicon substrate acting as the bottom-gate electrode. The solutionprocessed silicon oxide was prepared as described above. For the reference devices, the 230 nm SiO<sub>2</sub> was thermally grown. The indium-tin oxide/gold (ITO/Au) electrodes were prepared on the gate dielectric by UV lithography, sputtering (ITO), electron-beam evaporation (Au), and a lift-off technique. Therefore, a positive photoresist (AZ1514H, Micro Chemicals) was deposited by spincoating and exposed to UV light ( $\lambda = 365$  nm) through a photomask in a MJB 3 mask aligner from SUSS Micro Tec. The photoresist was developed using the AZ Developer from Micro Chemicals. The samples were pretreated in the ozone cleaner for 10 min. The solid indium-based metal oxo-alkoxide precursor (iXsenic S, Evonik Industries AG) was spin-coated under atmospheric conditions at 4000 rpm for 30 s and annealed at 350  $^\circ \mathrm{C}$  for 1 h. Outside of the active channel region, the metal oxide film was removed by conventional UV lithography and wet etching in oxalic acid (c = 1mol/L). The acid was heated to T = 50 °C to decrease the etching time to 10 min. The channel width to channel length ratio (W/L) was 200/20.

The layer thickness and refractive index of the oxide film were estimated from ellipsometry using a Sentech Sen-pro ellipsometer. The extracted layer thickness was compared with values taken from atomic force microscopy (AFM; Nanosurf, Mobile S). The depth of a groove in the solution-processed silicon oxide was measured to obtain the layer thickness. Microscope and scanning electron microscopy (SEM) micrographs were taken using a Leica DM 2500 M optical microscope and a Phenom scanning electron microscope from PEI, respectively. To extract the permittivity of the dielectric material, capacitance-voltage (C-V) measurements were done using an Agilent E4980 A LCR meter. For the current-voltage (I-V)characteristics of the TFTs and MIS structures, a semiconductor parameter analyzer (Agilent 4156B) was used. The fabricated TFTs were characterized under a nitrogen atmosphere at T = 300 K to avoid any influence from the ambient environment on the transistor performance.

# RESULTS AND DISCUSSION

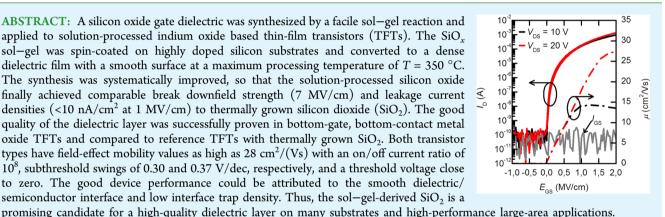

First of all, the film thickness and topography were investigated depending on the TEOS precursor concentration in the solution. The ratio between water and the TEOS precursor was kept constant to control the hydrolysis reaction. In order to decrease the total TEOS concentration, the solution was diluted with IPA. Film cracking is a problem, while the sol–gel coating is dried. Tensile stress during the drying and thermal treatment can lead to cracks if the film thickness exceeds a critical thickness.<sup>30</sup> Figure 1 shows optical micrographs of SiO<sub>x</sub>

**Figure 1.** Optical micrographs of solution-processed SiO<sub>x</sub> layers. The TEOS concentration within the solution amounts (a) c = 0.9 mol/L and (b) c = 0.8 mol/L, respectively.

films, which were prepared from solutions containing a TEOS concentration of 0.9 mol/L (Figure 1a) and 0.8 mol/L (Figure 1b), respectively. Figure 1a shows cracks in the dielectric layer after annealing, which primarily occur at the edges of the substrate. At the edges, the film thickness is increased, leading to a larger number of cracks. With decreasing film thickness (i.e., lower TEOS concentration), the films turn into defect-free films (Figure 1b). Thus, the maximum concentration of TEOS in the solution was determined as c = 0.8 mol/L to avoid the creation of cracks in the film.

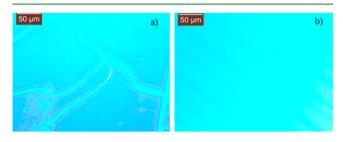

Figure 2a shows the resulting film thickness of the insulator after processing with respect to the TEOS concentration. The

**Figure 2.** (a) Film thickness of the  $SiO_x$  layers with respect to the TEOS concentration. (b) Leakage current density measured at 1 MV/ cm and a breakdown field strength for  $SiO_x$  layers with different TEOS precursor concentrations.

film thickness decreases (Figure 2b) from 180 nm (c = 1 mol/L) to 10 nm (c = 0.1 mol/L). Dielectric films prepared from a solution with a TEOS concentration higher than 0.3 mol/L exhibit a leakage current density of about  $2 \times 10^{-8} \text{ A/} \text{ cm}^2$  (Figure 2b) and a breakdown field strength above 7 MV/ cm (no breakdown was observed for concentrations above 0.8 mol/L). The leakage current density was extracted at an applied electric field of 1 MV/cm.

With decreasing TEOS concentration, the leakage current density increases to values larger than  $1 \times 10^{-6}$  A/cm<sup>2</sup> and the

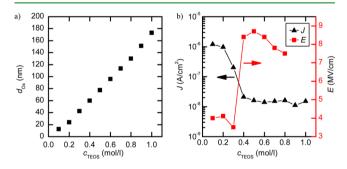

breakdown field strength drops to values of about 3–4 MV/cm. A topographical characterization of the films with AFM and SEM gives us a better understanding of this phenomenon. The films processed from solutions containing a precursor concentration of less than 0.3 mol/L show large holes in the dielectric layers (Figure 3).

Figure 3. (a) Top-view AFM micrograph and (b) SEM micrograph of a SiO<sub>x</sub> surface derived from a TEOS–sol solution containing a TEOS precursor concentration of 0.3 mol/L.

These holes have a diameter of around 5  $\mu$ m a typical depth of 50 nm, and we find around one or two of these holes in an area of 20  $\mu$ m  $\times$  20  $\mu$ m. The value of 50 nm corresponds to the total thickness of the dielectric layer derived from a sol-gel solution containing a TEOS concentration of 0.3 mol/L. We assume that these holes are generated by evaporation of the solvent during the annealing process. Around the holes, the thickness of the dielectric layer is much lower, and hot spots of the applied electric field are created during the electrical measurement. This explains the increase of the leakage current density and the reduced breakdown field strength. Holes are also observed for films prepared from solutions with higher TEOS concentrations, but the diameter and depth of the holes are reduced, which explains the improved dielectric properties. Here the holes have a typical diameter of 100 nm and a depth of about 8 nm, which is much smaller than the total thickness  $(d \gg 60 \text{ nm})$ . We find around 10 holes in an area of 2  $\mu$ m × 2  $\mu$ m. The surface roughness of the solution-processed SiO<sub>x</sub> in areas where no holes are located amounts to 0.6 nm and is comparable to the surface roughness of thermally grown SiO<sub>2</sub>  $(R_q = 0.5 \text{ nm})$ . These preliminary examinations show that for application as a gate dielectric in electronic devices the film thickness of the solution-processed SiO<sub>x</sub> should be between 60 and 150 nm.

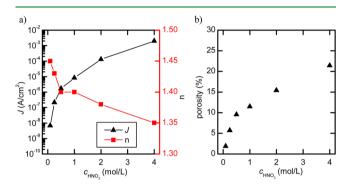

An important key parameter in the sol-gel chemistry is the pH value of the solution. It has a strong influence on the condensation and hydrolysis rates as well as on the structural properties of the final product.<sup>31</sup> In this study, we chose an acid-catalyzed sol-gel process. The pH value was controlled by the molarity of nitric acid. To get better insight into the chemistry, different silicia xerogels were prepared with different molarities of nitric acid ranging between 0.01 and 4.0 mol/L. The TEOS concentration (c = 0.8 mol/L), as well as the TEOS-to-H<sub>2</sub>O ratio, was kept constant. The gelation time for all solutions was 7 h. Before the spin-coating process, the solutions were filtered through a 0.2  $\mu$ m poly-(tetrafluorethylene) syringe filter. For the lowest molarity of the appointed nitric acid (0.01 mol/L), no film formation on the silicon substrates was observable after the spin-coating and annealing process. The acid acts as a catalyst for the sol-gel reaction, which is a combination of hydrolysis and condensation reactions. The aging time of 7 h is too short for the low molarity of nitric acid to form Si–O–Si bonds by hydrolysis and condensation. For higher acidities, SiO<sub>x</sub> colloids or network structures have already grown so that dielectric films are formed on the substrates. The thickness of the films varies between 142 nm ( $c_{\rm HNO_3} = 0.1 \text{ mol/L}$ ) and 152 nm ( $c_{\rm HNO_3} = 4.0 \text{ mol/L}$ ). The leakage current density and refractive index were investigated with respect to the molarity of the acid. Figure 4a shows an increase of the leakage current density with

**Figure 4.** (a) Leakage current density at 1 MV/cm and refractive index for different  $SiO_x$  layers made from TEOS–sol solutions containing a HNO<sub>3</sub> concentration between 0.1 and 4 mol/L. (b) Derived porosity from the measured refractive index by the Lorentz–Lorenz relationship.

increasing molarities of nitric acid, while the refractive index decreases. The smaller refractive index indicates a higher porosity. A higher porosity leads to an increase of trap states within the dielectric layer. The trap states tend to enhance the Poole–Frenkel conduction mechanism,<sup>22</sup> which dominates the conduction at higher electric fields, as we will see later. The film porosity *P* was determined by the Lorentz–Lorenz equation:<sup>32</sup>

$$\frac{n^2 - 1}{n^2 + 2} = (1 - P)\frac{n_0^2 - 1}{n_0^2 + 2}$$

Here,  $n_0$  is the refractive index of the dense SiO<sub>2</sub> ( $n_0 = 1.460$ ).

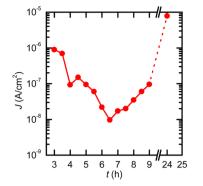

The porosity of the film increases from 2% to 21% with an increasing amount of catalyst (Figure 4b). We assume that the higher concentration of nitric acid results in an accelerated gelation process and consequently in larger network structures. In these networks, liquids are encapsulated in small pores, which evaporate during the thermal treatment of the film. Thus, the porosity increases. It is important to control the gelation of the sol. In principle, the gelation of the sol can be influenced by the concentration of the catalyst or by the gelation time because a higher concentration of the catalyst leads to higher leakage current densities (Figure 4). The influence of the gelation time for a solution with the lowest possible concentration of the catalyst ( $c_{HNO_3} = 0.1 \text{ mol/L}$ ) was examined below. Figure 5 shows the current density with respect to the gelation time of a sol-gel solution containing nitric acid with a concentration of  $c_{\text{HNO}_3} = 0.1 \text{ mol/L}$ . The findings indicate that the gelation time plays an important role in the sol-gel process. For solutions with gelation time of less than 3 h, it was not possible to form a silicon oxide film on the substrate. The first investigated silicon oxide layer with a gelation time of 3 h exhibits a leakage current density of about 1  $\mu$ A/cm<sup>2</sup>. The leakage current density decreases by 2 orders of magnitude for solutions, which gelatinize for 7 h. It was found that a gelation time of 6-7 h is

**Figure 5.** Leakage current density at 1 MV/cm for a  $SiO_x$  layer prepared from a solution with a TEOS precursor concentration of 0.8 mol/L and a HNO<sub>3</sub> concentration of 0.1 mol/L measured after different aging times (3–24 h). The red line has no physical meaning. It is only a guide for the eye.

the optimal time for this solution. After 7 h, the leakage current density increases with the aging time.

The decrease of the leakage current density within the first 7 h can be explained by the formation of siloxane (Si-O-Si) structures, which are necessary to form dense silicon oxide layers on the substrate. During the gelation, the network structure grows and small pores are created with water or alcohol containments. These liquids evaporate during the annealing process. In this way, current paths are formed in the dielectric layer, and they lead to an increase of the leakage current density. For the hydrolysis and condensation reaction, the structure of the gel is dependent on the time of gelation.<sup>33</sup> First of all, small particles are formed that are dispersed in the liquid, which is called a sol. These particles agglomerate to form a three-dimensional network of Si-O-Si bonds and is designated as a gel. We assume that the leakage current density increases when the gelation starts and the network structure begins to grow. Defects in the dielectric layer are created during the annealing process. If an electric field is applied, the charge carriers will move along the defect paths. With increasing electric field, additional defects are created and percolation paths are formed. Thus, the leakage current density increases.<sup>3</sup>

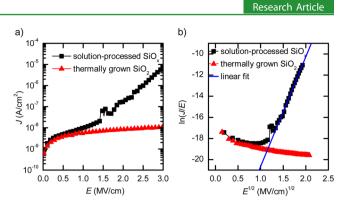

After optimization of the sol-gel solution and process parameters, it is necessary to investigate the suitability of the solution-processed silicon oxide as a gate dielectric. We compared the leakage current density and permittivity of the solution-processed SiO<sub>r</sub> layer with a 230-nm-thick thermally grown SiO<sub>2</sub> layer. Figure 6a shows the leakage current density with respect to the applied electric field of the solutionprocessed silicon oxide compared to the thermally grown SiO<sub>2</sub>. The solution contains nitric acid as the catalyst ( $c_{\text{HNO}_2} = 0.1$ mol/L), has a TEOS concentration of c = 0.8 mol/L, and was aged for about 6.5 h. The resulting thickness of the oxide amounts to 143 nm. The current density in the solutionprocessed oxide at an electric field of 1 MV/cm is about 7 ×  $10^{-9}$  A/cm<sup>2</sup>, which is similar to the thermally grown dielectric. At an applied field of 1.5 MV/cm, the current density of the solution-processed SiO<sub>r</sub> starts to increase more over the applied electric field. We believe that the Poole-Frenkel conduction mechanism dominates for higher electric fields. The Poole-Frenkel mechanism can be mathematically described by

**Figure 6.** (a) Field-dependent leakage current density for a 143-nmthick solution-processed  $SiO_x$  layer (black squares) and a 230 nm thermally grown  $SiO_2$  layer (red triangles). (b) Poole–Frenkel plot for the solution-processed silicon oxide.

$$J_{\rm PF} = q N_{\rm t} \mu E \, \exp \! \left[ -\frac{1}{kT} \! \left( q \phi_{\rm B} - \sqrt{\frac{q^3 E}{\pi \varepsilon_0 \varepsilon_{\rm r}}} \right) \right]$$

Here q,  $N_t$ ,  $\mu$ ,  $q\phi_{\rm B}$ , and  $\varepsilon_{\rm r}$  denote the elementary charge, trap density, carrier mobility, barrier height of the traps, and dielectric constant of the oxide, respectively. Therefore, the Poole–Frenkel mechanism is dominant when the  $\ln(I/E)$ versus  $E^{1/2}$  is linear.<sup>35</sup> This is the case for the solutionprocessed SiO<sub>x</sub> for  $E^{1/2} > 1.0$  MV/cm but not for the thermally grown SiO<sub>2</sub> over the hole sweep range (Figure 6b). If the current flow is dominated by trap states, the barrier height between the trap states is lowered with increasing electric field. Thus, the charge carriers can move more easily from trap state to trap state. We conclude that the trap states are due to the higher porosity of the solution-processed dielectric compared to the thermally grown SiO<sub>2</sub>. For a conversion temperature of  $T = 250 \,^{\circ}$ C, the leakage current density increases by 2 orders of magnitude at E = 1 MV/cm (Figure S1 in the Supporting Information, SI). For applications on flexible substrates, the process must be further improved by using nonthermal conversion techniques, e.g., oxygen plasma treatment.<sup>36</sup>

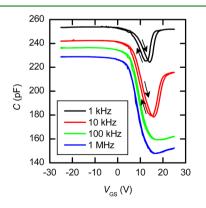

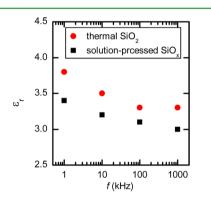

The permittivity  $\varepsilon_r$  of the solution-processed SiO<sub>x</sub> was calculated from C-V measurements, which are shown in Figure 7. The measurements were performed at different frequencies ranging from 1 kHz to 1 MHz. Prior to any C-V studies, the leakage current through the MIS devices was measured. In this

**Figure 7.** C-V hysteresis of a solution-processed silicon oxide film at different frequencies (black, 1 kHz; red, 10 kHz; green, 100 kHz; blue, 1 MHz).

regard, typical leakage currents were found to be on the order of  $10^{-11}$  A.

For low frequencies (f = 1 and 10 kHz), the C-V characteristics show clockwise hysteresis of about 2 and 1 V, respectively, which can be explained by the presence of trap states at the Si/SiO<sub>x</sub> interface. At higher frequencies, the hysteresis disappears because the charge process of the trap states is too slow.<sup>37</sup> The permittivity is derived from the maximum capacitance in the accumulation regime, where the series capacitance of the depletion zone is negligible and the measured value corresponds to the oxide capacitance. The relationship between the capacitance and permittivity is given by the following equation:

$$C = \frac{\varepsilon_0 \varepsilon_r A}{d}$$

where *C* is the measured capacitance in the accumulation regime,  $\varepsilon_0 = 8.854 \times 10^{-12} \text{ (A s)}/(\text{V m})$  is the permittivity of the vacuum, *A* is the contact area, and *d* is the thickness of the dielectric layer. The derived frequency-dependent permittivities for both the solution-processed and thermally grown SiO<sub>2</sub> are illustrated in Figure 8.

**Figure 8.** Derived frequency-dependent permittivities for the solutionprocessed  $SiO_x$  (black squares) and thermally grown  $SiO_2$  (red circles).

The calculated permittivity of the solution-processed silicon oxide is in the range of the permittivity of the thermally grown oxide. We assume that the slightly lower permittivity results from residuals within the layer and from a higher porosity.

The low leakage current density and high electric breakdown field strength make the sol-gel-derived silicon oxide suitable for use as a gate dielectric in a TFT. Therefore, we used this dielectric combined with the solution-processed semiconductor iXsenic S in bottom-gate, bottom-contact TFTs (sample A) and compared the results with TFTs containing a thermally grown SiO<sub>2</sub> acting as a gate dielectric (sample B).

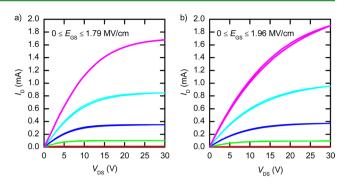

Typical output characteristics of transistors with a solutionprocessed and thermally grown  $SiO_x$  dielectric layer are displayed in Figure 9. Both transistors show similar characteristics. The TFT of sample A exhibits clear current saturation and pinch-off behavior, indicating that the entire thickness of the semiconductor channel layer can be depleted of free electrons. The transistor with thermally grown  $SiO_2$  shows no clear saturation for higher gate voltages, which may result from the different oxide thicknesses.

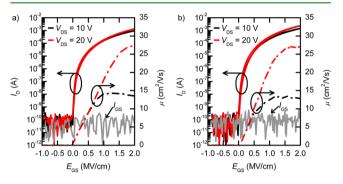

Figure 10 displays the source–drain current  $I_{DS}$  and the mobility  $\mu$  as a function of the electric field for typical TFTs of both samples. The transfer characteristics were measured at two

Research Article

**Figure 9.** Output characteristics of bottom-contact transistors with (a) a 143-nm-thick solution-processed  $SiO_x$  gate dielectric and (b) a 230-nm-thick thermally grown  $SiO_2$  gate dielectric.

**Figure 10.** Transfer characteristics (solid line) and mobility versus the electric field  $E_{GS}$  (dash-dotted line) of a TFT with (a) a 143-nm-thick solution-processed insulator and (b) a 230 nm thermally grown SiO<sub>2</sub> layer. Furthermore, the leakage current  $I_{GS}$  through the dielectric layer is shown as a gray line.

different source–drain voltages,  $V_{\rm DS1} = 10$  V and  $V_{\rm DS2} = 20$  V. The gate voltage of sample A was swept between -20 and +30 V. Taking into account the higher thickness of the thermally grown SiO<sub>2</sub>, the gate voltage for sample B was varied from -20 to +50 V. Hence, the electric field in sample B is comparable to the field generated in sample A. The solution-processed semiconductor iXsenic S works as an n-channel device, as can be seen from Figures 9 and 10. Both TFTs show a good on/off ratio of about  $10^8$ , an onset voltage close to zero, and no hysteresis, indicating that no charge trapping in the bulk of the semiconductor or at the semiconductor/dielectric interface occurs. The mobility was calculated from the first derivative of the square root of the drain–source current:

$$\mu_{\rm sat.} = \frac{2L}{WC_{\rm i}} \left(\frac{\partial \sqrt{I_{\rm DS}}}{\partial V_{\rm GS}}\right)^2$$

Here, *L* and *W* denote the channel length and width of the transistors and  $C_i$  the gate dielectric capacitance per unit area. The derived mobility values are 14 cm<sup>2</sup>/(Vs) for  $V_{DS1} = 10$  V and 28 cm<sup>2</sup>/(Vs) for  $V_{DS2} = 20$  V. These values of the mobility are an upper limit because we used the dielectric constant for *f* = 1 kHz. The electrical parameters of the TFTs are comparable to recently achieved parameters based on solution-processed indium oxide TFTs.<sup>38–46</sup> (Further details given in Table S1 in the SI.)

The interface trap charge density  $N_{\rm s}$  is directly related to the subthreshold swing  $S_{\rm sub}$  by the following relationship:<sup>47</sup>

# ACS Applied Materials & Interfaces

$$N_{\rm s}^{\rm max} = \left(\frac{S_{\rm sub}\log e}{kT/q} - 1\right)\frac{C_{\rm i}}{q}$$

Here, q is the electronic charge, k the Boltzmann constant, and T the absolute temperature. The subthreshold swing  $S_{sub}$  is extracted from the inverse of the maximum slope of the transfer characteristic. It indicates the gate voltage  $V_{GS}$ , which is required to increase  $I_{DS}$  by 1 decade.

$$S_{\rm sub} = \left[\frac{d \log(I_{\rm DS})}{dV_{\rm GS}}\Big|_{\rm max}\right]^{-1}$$

The subthreshold swing of the TFT from sample A (sample B) is around 0.30 V/dec (0.37 V/dec), which corresponds to a maximum interface trap density of  $5.5 \times 10^{11}$  cm<sup>-2</sup> ( $5.9 \times 10^{11}$  cm<sup>-2</sup>). We believe the low interface trap density of the solution-processed silicon oxide is due to the smooth surface. The gate leakage current  $I_{\rm GS}$  is also drawn in Figure 9 (gray lines). The leakage current of both devices is over the whole sweep range of  $V_{\rm GS}$  below the noise level (100 pA) of the measurement equipment. The nearly identical electrical properties of the transistors underline the excellent quality of the solution-processed SiO<sub>xy</sub> which is at least equivalent to thermally grown SiO<sub>2</sub>.

# CONCLUSIONS

We developed a high-quality solution-processed silicon oxide for TFT applications by a facile sol-gel reaction. We demonstrated the importance of the TEOS precursor concentration in the sol-gel solution to avoid film cracking and pinhole creation during the annealing process. The leakage current density and electric breakdown field strength were drastically improved by optimizing the catalyst content and gelation time. Optimal dielectric properties were achieved with a sol-gel solution containing nitric acid as the catalyst ( $c_{HNO_2}$  = 0.1 mol/L), a TEOS concentration of c = 0.8 mol/L, and a gelation time of 6.5 h. The applicability of the sol-gel solution was verified by metal oxide TFTs prepared with the solutionprocessed SiO<sub>x</sub> and a solution-processed indium-based metal oxide. They exhibit a field-effect mobility of 28 cm<sup>2</sup>/(Vs), an on/off ratio of  $10^8$ , no hysteresis, an onset voltage close to zero, and a small interface trap density  $(5.9 \times 10^{11} \text{ cm}^{-2})$ . The obtained electrical properties of the TFTs with solutionprocessed silicon oxide are at least equivalent to those with thermally grown SiO<sub>2</sub>. Because thermally grown SiO<sub>2</sub> requires a silicon substrate, the solution-processed silicon oxide has a decisive advantage. It can be used on many other substrates, e.g., glass or compound semiconductors. The first results were achieved on a glass substrate (Figure S2 in the SI).

# ASSOCIATED CONTENT

#### **S** Supporting Information

Leakage current density for the solution-processed silicon oxide at a maximum temperature of 250 °C, recently published mobility values for solution-processed indium oxide based TFTs, and leakage current density for the solution-processed silicon oxide coated on glass/ITO substrates. The Supporting Information is available free of charge on the ACS Publications website at DOI: 10.1021/acsami.5b03105.

## AUTHOR INFORMATION

#### **Corresponding Author**

\*E-mail: felix.jaehnike@rub.de.

#### Notes

The authors declare no competing financial interest.

#### REFERENCES

(1) Sun, J.; Zhang, B.; Katz, H. E. Materials for Printable, Transparent, and Low-Voltage Transistors. *Adv. Funct. Mater.* 2011, 21, 29–45.

(2) Kim, M.-G; Kanatzidis, M. G.; Facchetti, A.; Marks, T. J. Low-Temperature Fabrication of High-Performance Metal Oxide Thin-Film Electronics via Combustion Processing. *Nat. Mater.* **2011**, *10*, 382– 388.

(3) Avis, C.; Jang, J. High-Performance Solution Processed Oxide TFT with Aluminum Oxide Gate Dielectric fabricated by a Sol–Gel Method. J. Mater. Chem. 2011, 11, 10649–10652.

(4) Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-Temperature Fabrication of transparent flexible Thin-Film Transistors using Amorphous Oxide Semiconductors. *Nature* **2004**, *432*, 488–492.

(5) Park, J. S.; Maeng, W.-J.; Kim, H. S.; Park, J.-S. Review of Recent Developments in Amorphous Oxide Semiconductor Thin-Film Transistor Devices. *Thin Solid Films* **2012**, *520*, 1679–1693.

(6) Fortunato, E.; Barquinha, P.; Martins, R. Oxide Semiconductor Thin-Film Transistors: A Review of Recent Advances. *Adv. Mater.* **2012**, *24*, 2945–2986.

(7) Weber, D.; Botnaras, S.; Pham, D. V.; Merkulov, A.; Steiger, J.; Schmechel, R.; De Cola, L. A Facile Solution-Doping Method to Improve a Low-Temperature Zinc Oxide Precursor: Towards Low-Cost Electronics on Plastic Foil. *Adv. Funct. Mater.* **2014**, *24*, 2537– 2543.

(8) Wager, J. F.; Yeh, B.; Hoffmann, R. L.; Keszler, D. A. An Amorphous Oxide Semiconductor Thin-Film Transistor Route to Oxide Electronics. *Curr. Opin. Solid State Mater. Sci.* **2014**, *18*, 53–61.

(9) Koo, C. Y.; Song, K.; Jung, Y.; Yang, W.; Kim, S.-H.; Jeong, S.; Moon, J. Enhanced Performance of Solution-Processed Amorphous LiYInZnO Thin-Film Transistors. *ACS Appl. Mater. Interfaces* **2012**, *4*, 1456–1461.

(10) Hennek, J. W.; Kim, M.-G.; Kanatzidis, M. G.; Facchetti, A.; Marks, T. J. Exploratory Combustion Synthesis: Amorphous Indium Yttrium Oxide for Thin-Film Transistors. *J. Am. Chem. Soc.* **2012**, *134*, 9593–9596.

(11) Xu, X.; Feng, L.; He, S.; Jin, Y.; Guo, X. Solution-Processed Zinc Oxide Thin-Film Transistors with a Low-Temperature Polymer Passivation Layer. *IEEE Electron Device Lett.* **2012**, *33*, 1420–1422.

(12) Song, K.; Yang, W.; Jung, Y.; Jeong, S.; Moon, J. A Solution-Processed Yttrium Oxide Gate Insulator for High-Performance All-Solution-Processed fully Transparent Thin Film Transistors. *J. Mater. Chem.* **2012**, *22*, 21265.

(13) Liu, A.; Liu, G. X.; Zhu, H. H.; Xu, F.; Fortunato, E.; Martins, R.; Shan, F. K. Fully Solution-Processed Low-Voltage Aqueous  $In_2O_3$ Thin-Film Transistors Using an Ultrathin  $ZrO_x$  Dielectric. *ACS Appl. Mater. Interfaces* **2014**, *6*, 17364–17369.

(14) Xu, W.; Wang, H.; Ye, L.; Xu, J. The Role of Solution-Processed High- $\kappa$  Gate Dielectrics in Electrical Performance of Oxide Thin-Film Transistors. *J. Mater. Chem. C* **2014**, *2*, 5389–5396.

(15) Jeong, S.; Lee, J.-Y.; Ham, M.-H.; Song, K.; Moon, J.; Seo, Y.-H.; Ryu, B.-H.; Choi, Y. Bendable Thin-Film Transistors based on Sol–Gel derived Amorphous Ga-doped  $In_2O_3$  Semiconductors. *Superlattices Microstruct.* **2013**, *59*, 21–28.

(16) Lee, Y.-G.; Choi, W.-S. Effect of Aluminum Doping on a Solution-Processed Zinc-Tin-Oxide Thin-Film Transistor. *Electron. Mater. Lett.* **2013**, *9*, 719–722.

(17) Kim, G. H.; Ahn, B. D.; Shin, H. S.; Jeong, W. H.; Kim, H. J.; Kim, H. J. Effect of Indium Composition Ratio on Solution-Processed Nanocrystalline InGaZnO Thin Film Transistors. *Appl. Phys. Lett.* **2009**, *94*, 233501–1–233501–3.

## **ACS Applied Materials & Interfaces**

(19) Blanchin, M.-G.; Canut, B.; Lambert, Y.; Teodorescu, V. S.; Barau, A.; Zaharescu, M. Structure and Dielectric Properties of HfO<sub>2</sub> Films prepared by a Sol–Gel Route. *J. Sol–Gel Sci. Technol.* **2008**, 47, 165–172.

(20) Aoki, Y.; Kunitake, T. Solution-based Fabrication of High-κ Gate Dielectrics for Next-Generation Metal-Oxide Semiconductor Transistors. *Adv. Mater.* **2004**, *16*, 118–123.

(21) Tu, H. T. C.; Inoue, S.; Tue, P. T.; Miyasako, T.; Shimoda, T. Investigation of Polysilazane-Based SiO<sub>2</sub> Gate Insulator for Oxide Semiconductor. Thin-Film Transistors. *IEEE Trans. Electron Devices* **2013**, *60*, 1149–1153.

(22) Liu, P.-T.; Chang, T. C.; Hsu, K. C.; Tseng, T. Y.; Chen, L. M.; Wang, C. J.; Sze, S. M. Characterization of Porous Silicate for Ultralow k Dielectric Application. *Thin Solid Films* **2002**, *414*, 1–6.

(23) Vishwas, M.; Rao, K. N.; Phani, A.; Gowda, K. A.; Chakradhar, R. Spectroscopic and electrical properties of  $SiO_2$  films prepared by simple and cost effective sol-gel process. *Spectrochim. Acta, Part A* **2011**, 78, 695–699.

(24) Cavas, M.; Al-Ghamdi, A. A.; Al-Hartomy, O. A.; El-Tantawy, F.; Yakuphanoglu, F. A Pentacene Thin Film Transistor with Good Performance Using Sol–Gel derived SiO<sub>2</sub> Gate Dielectric Layer. *Solid State Sci.* **2013**, *16*, 111–116.

(25) www.iXsenic.com.

(26) Jaehnike, F.; Hoppe, A.; Pham, D. V.; Steiger, J. High Performance, Stable Solution-Processed Thin-Film Transistors. *SPIE Newsroom Illumination Display* **2012**.

(27) Rockelé, M.; Pham, D. V.; Steiger, J.; Botnaras, S.; Weber, D.; Vanfleteren, J.; Serken, T.; Cuypers, D.; Steudel, S.; Myny, K.; Schols, S.; van der Putten, B.; Genoe, J.; Heremans, P. Solution-Processed and Low-Temperature Metal Oxide n-Channel Thin-Film Transistors and Low-Voltage Complementary Circuitry on Large-Area flexible Polyimide Foil. J. Soc. Inf. Disp. 2012, 20, 499–507.

(28) Steiger, J.; Pham, D. V.; Marinkovic, M.; Hoppe, A.; Neumann, A.; Anselmann, R. Development of Low Temperature Solution-Processed Metal-Oxide TFT Materials; IDW Publishing: San Diego, CA, 2012.

(29) Weber, C.; Oberberg, M.; Weber, D.; Bock, C.; Pham, D. V.; Kunze, U. Improved Morphology and Performance of Solution-Processed Metal-Oxide Thin-Film Transistors due to a Polymer based Interface Modifier. *Adv. Mater. Interfaces* **2014**, *7*, 1400137.

(30) Guglielmi, M. Sol-Gel Coatings on Metals. J. Sol-Gel Sci. Technol. 1997, 8, 443-449.

(31) Siouffi, A.-M. Silica Gel-based Monoliths Prepared by the Sol-Gel Method: Facts and Figures. *J. Chromatogr. A* **2003**, *1000*, 801–818.

(32) Mezza, P.; Phalippou, J.; Sempere, R. Sol–Gel derived porous Silica Films. J. Non-Cryst. Solids 1999, 243, 75–79.

(33) Hench, L. L.; West, J. K. The Sol-Gel Process. Chem. Rev. 1990, 90, 33-72.

(34) Bentarzi, H. Transport in Metal-Oxide-Semiconductor Structures; Springer: Berlin, 2011.

(35) Cheong, K. Y.; Moon, J. H.; Kim, H. J.; Bahng, W.; Kim, N.-K. Current Conduction Mechanisms in Atomic-Layer-Deposited HfO<sub>2</sub>/Nitride SiO<sub>2</sub> Stacked Gate on 4H Silicon Carbide. *J. Appl. Phys.* 2008, 103, 084113.

(36) Jeong, Y.; Pearson, C.; Kim, H.-G.; Park, M.-Y.; Kim, H.; Do, L.-M.; Petty, M. C. Solution-Processed SiO<sub>2</sub> Gate Insulator at Low Temperature for Zinc Oxide Thin-Film Transistors. *RSC Adv.* **2015**, *5*, 36083–36087.

(37) Sze, M. S. *Physics of Semiconductor Devices*; John Wiley and Sons: New York, 2007.

(38) Yu, X.; Zeng, L.; Zhou, N.; Guo, P.; Shi, F.; Buchholz, D. B.; Ma, Q.; Yu, J.; Dravid, V. P.; Chang, R. P. H.; Bedzyk, M.; Marks, T. J.; Facchetti, A. Ultra-Flexible, "Invisible" Thin-Film Transistors Enabled by Amorphous Metal Oxide/Polymer Channel Layer Blends. *Adv. Mater.* **2015**, *27*, 2390–2399. (39) Meng, Y.; Liu, G.; Liu, A.; Song, H.; Hou, Y.; Shin, B.; Shan, F. Low-Temperature Fabrication of High Performance Indium Oxide Thin Film Transistors. *RSC Adv.* **2015**, *5*, 37807–37813.

(40) Kim, H. J.; Je, S. Y.; Won, J. Y.; Baek, J. H.; Jeong, J. K. Effect of Antimony Doping on the Low-Temperature Performance of Solution-Processed Indium Oxide Thin Film Transistors. *Phys. Status Solidi RRL* **2014**, *8*, 924–927.

(41) Choi, C.-H.; Han, S.-Y.; Su, Y.-W.; Fang, Z.; Lin, L.-Y.; Cheng, C.-C.; Chang, C.-h. Fabrication of High-Performance, Low-Temperature Solution Processed Amorphous Indium Oxide Thin-Film Transistors Using Volatile Nitrate Precursor. J. Mater. Chem. C 2015, 3, 854–860.

(42) Hwang, Y. H.; Seo, J.-S.; Yun, J. M.; Park, H.; Yang, S.; Park, S.-H. K.; Bae, B.-S. An 'Aqueous Route' for the Fabrication of Low-Temperature-Processed Oxide Flexible Transparent Thin-Film Transistors on Plastic Substrates. *NPG Asia Mater.* **2013**, *5*, 1–8.

(43) Yu, X.; Smith, J.; Zhou, N.; Zeng, L.; Guo, P.; Alvarez, A.; Aghion, S.; Lin, H.; Yu, J.; Chang, R. P. H.; Bedzyk, M. J.; Ferragut, R.; Marks, T. J.; Faccetti, A. Spray-Combustion Synthesis: Efficient Solution Route to High-Performance Oxide Transistors. *Proc. Natl. Acad. Sci. U.S.A.* **2015**, *112*, 3217–3222.

(44) Liu, A.; Liu, G. X.; Zhu, H. H.; Xu, F.; Fortunato, E.; Martins, R.; Shan, F. K. Fully Solution-Processed Low-Voltage Aqueous  $In_2O_3$ Thin-Film Transistors Using an Ultrathin  $ZrO_x$  Dielectric. ACS Appl. Mater. Interfaces 2014, 6, 17364–17369.

(45) Xu, W.; Wang, H.; Xie, F.; Chen, J.; Cao, H.; Xu, J.-B. Facile and Environmentally Friendly Solution-Processed Aluminum Oxide Dielectric for Low-Temperature, High-Performance Oxide Thin-Film Transistors. *ACS Appl. Mater. Interfaces* **2015**, *7*, 5803–5810.

(46) Nayak, P. K.; Hedhili, M. N.; Cha, D.; Alshareef, H. N. High Performance  $In_2O_3$  Thin Film Transistors Using Chemically Derived Aluminum Oxide Dielectric. *Appl. Phys. Lett.* **2013**, *103* (033518), 1–4.

(47) Kim, K.-S.; Lee, S.-W.; Oh, S.-M.; Cho, W. J. Development of Annealing Process for Solution-Derived High Performance InGaZnO Thin-Film Transistors. *Mater. Sci. Eng. B* 2013, *178*, 811–815.